一👼、程序查詢方式

程序查詢方式的工作流程如下:

CPU執行初始化程序,並預置傳送參數。

向 I/O接口發出命令字,啟動I/O 設備。

從外設接口讀取其狀態信息🕵🏻♂️。

CPU不斷查詢 I/O 設備狀態,直到外設准備就緒。

傳送一次數據。

修改地址和計數器參數✍🏿。

判斷傳送是否結束,若未結束轉第③步,直到計數器為0🤙✵。

在這種控制方式下,CPU一旦啟動 I/O,就必須停止現行程序的運行,並在現行程序中插入一段程序🍽。程序查詢方式的主要特點是 CPU有“踏步”等待現象,CPU 與I/O串行工作。這種方式的接口設計簡單、設備量少,但CPU在信息傳送過程中要花費很多時間來查詢和等待,而且在一段時間內只能和一臺外設交換信息,效率大大降低👩🦱。

在程序查詢方式的輸入/輸出系統中,假設不考慮處理時間,每一個查詢操作需要100個時鐘周期,CPU的時鐘頻率為50MHz。現有鼠標和硬盤兩個設備,而且CPU必須每秒對鼠標進行30次查詢,硬盤以32位字長為單位傳輸數據,即每32位被CPU查詢一次,傳輸率為2×22B/s。求CPU對這兩個設備查詢所花費的時間比率,由此可得出什麼結論?

CPU一旦啟動I/O,必須停止現行程序的運行,並在現行程序中插入一段程序🙅🏽♀️。

主要特點🧑🎤:CPU有“踏步”等待現象🧑🏿🎨,CPU與I/O串行工作🤟🏻。

優點:接口設計簡單🏊🏽、設備量少。

缺點:CPU在信息傳送過程中要花費很多時間用于查詢和等待,而且如果采用獨占查詢,則在一段時間內只能和一臺外設交換信息🧑🏻✈️,效率大大降低♜。

獨占查詢:CPU 100%的時間都在查詢I/O狀態🤵🏿♀️,完全串行

定時查詢:在保證數據不丟失的情況下🥧,每隔一段時間CPU就查詢一次 I/O狀態。查詢的間隔內CPU可以執行其他程序🏃🏻♀️➡️。

二、程序中斷方式

(一)、中斷系統

中斷的基本概念

程序中斷是指在計算機執行現行程序的過程中,出現某些急需處理的異常情況或特殊請求,CPU暫時中止現行程序,而轉去對這些異常情況或特殊請求進行處理📤,在處理完畢後CPU又自動返回到現行程序的斷點處🎷,繼續執行原程序🌖。

工作流程🫲🏻:

中斷請求

中斷源向CPU發送中斷請求信號。

中斷響應

響應中斷的條件🩱。

中斷判優:多個中斷源同時提出請求

時通過中斷判優邏輯響應一個中斷源。

中斷處理

中斷隱指令。

中斷服務程序。

中斷請求的分類

IF:Interrupt Flag📳,存在PSW中,

IF=1表示開中斷(允許中斷)

IF=0表示關中斷(不允許中斷)

中斷請求標記

如何判斷是哪個設備發來的中斷信號?

每個中斷源向CPU發出中斷請求的時間是隨機的。

為了記錄中斷事件並區分不同的中斷源,中斷系統需對每個中斷源設置中斷請求標記觸發器INTR,

當其狀態為“1”時,表示中斷源有請求。

這些觸發器可組成中斷請求標記寄存器❤️,該寄存器可集中在CPU中🚮,也可分散在各個中斷源中👩🏼🦳。

對于外中斷🚵🏿♂️,CPU是在統一的時刻即每條指令執行階段結束前向接口發出中斷查詢信號💆🏼♀️,以獲取I/O的中斷請求⛔,也就是說,CPU響應中斷的時間是在每條指令執行階段的結束時刻🧎♀️➡️。

CPU響應中斷必須滿足以下3個條件:

① 中斷源有中斷請求。

② CPU允許中斷即開中斷。

③ 一條指令執行完畢,且沒有更緊迫的任務。

中斷判優-實現

中斷判優用于判斷有多個中斷信號同時到來,先處理哪個?

中斷判優既可以用硬件實現🏬,也可用軟件實現:

中斷判優-優先級設置

硬件故障中斷屬于最高級🤽♀️,其次是軟件中斷;

非屏蔽中斷優于可屏蔽中斷🧖♂️;

DMA請求優于I/O設備傳送的中斷請求;

高速設備優于低速設備;

輸入設備優于輸出設備;

實時設備優于普通設備。

(二)、中斷處理過程

中斷處理過程-中斷隱指令

並不是一條具體的指令🪥,而是CPU在檢測到中斷請求時自動完成的一系列動作。

中斷隱指令的主要任務🤾🏻:

① 關中斷。在中斷服務程序中🤷🏼♀️,為了保護中斷現場(即CPU主要寄存器中的內容)期間不被新的中斷所打斷🕋🏊🏻♀️,必須關中斷,從而保證被中斷的程序在中斷服務程序執行完畢之後能接著正確地執行下去。

② 保存斷點。為了保證在中斷服務程序執行完畢後能正確地返回到原來的程序🥖,必須將原來程序的斷點(即程序計數器(PC)的內容)保存起來🤵🏽♀️。可以存入堆棧🐴,也可以存入指定單元🪲。

③ 引出中斷服務程序。引出中斷服務程序的實質就是取出中斷服務程序的入口地址並傳送給程序計數器(PC)。

中斷處理過程-硬件向量法

中斷處理過程-中斷服務程序

中斷服務程序的主要任務:

① 保護現場

保存通用寄存器和狀態寄存器的內容(eg:保存 ACC寄存器的值)🥖,以便返回原程序後可以恢複 CPU環境🦸🏿。可使用堆棧,也可以使用特定存儲單元。

② 中斷服務(設備服務)

主體部分,如通過程序控制需打印的字符代碼送入打印機的緩沖存儲器中(eg:中斷服務的過程中有可能修改ACC寄存器的值)

③ 恢複現場

通過出棧指令或取數指令把之前保存的信息送回寄存器中(eg🧑⚖️:把原程序算到一般的ACC值恢複原樣)

④中斷返回

通過中斷返回指令回到原程序斷點處🎽。

總結:中斷處理過程

(三)🧛🏼、多重中斷

單重中斷:執行中斷服務程序時不響應新的中斷請求🦦。

多重中斷🧑🚒:又稱中斷嵌套,執行中斷服務程序時可響應新的中斷請求。

(四)🚗、中斷屏蔽技術

中斷屏蔽技術主要用于多重中斷,CPU要具備多重中斷的功能,須滿足下列條件🧑🧒。

① 在中斷服務程序中提前設置開中斷指令。

② 優先級別高的中斷源有權中斷優先級別低的中斷源。

每個中斷源都有一個屏蔽觸發器,1表示屏蔽該中斷源的請求🧗🏻♀️,0表示可以正常申請➞,所有屏蔽觸發器組合在一起👨🏻🦱,便構成一個屏蔽字寄存器,屏蔽字寄存器的內容稱為屏蔽字。

屏蔽字設置的規律:

一般用‘1’表示屏蔽,’0’表示正常申請。

每個中斷源對應一個屏蔽字(在處理該中斷源的中斷服務程序時🤜,屏蔽寄存器中的內容為該中斷源對應的屏蔽字)。

屏蔽字中‘1’越多🙍🦹🏽♀️,優先級越高。每個屏蔽字中至少有一個’1’(至少要能屏蔽自身的中斷)🥮。

(五)、程序中斷過程

假定CPU主頻為50MHz🟧,CPI 為4。設備D采用異步串行通信方式向主機傳送7位ASCII字符,通信規程中有1位奇校驗位和1位停止位🔋,從 D 接收啟動命令到字符送入 I/O端口需要0.5ms。請回答下列問題,要求說明理由。

1)每傳送一個字符,在異步串行通信線上共需傳輸多少位?在設備D持續工作過程中🦹🏿♀️,每秒鐘最多可向 I/O端口送入多少個字符?

2)設備D采用中斷方式進行輸入/輸出,示意圖如下:

I/O端口每收到一個字符申請一次中斷,中斷響應需10個時鐘周期,中斷服務程序共有20條指令,其中第15條指令啟動D工作。若CPU需從D讀取1000個字符👨💻,則完成這一任務所需時間大約是多少個時鐘周期?CPU用于完成這一任務的時間大約是多少個時鐘周期?在中斷響應階段CPU進行了哪些操作?

至少包含1位起始位和1位停止位,停止位可能有多位✡︎♘。

每傳送一個字符需要傳送1位起始位👩🌾、7位數據位、1位校驗位🧛🏿♀️、1位停止位,共需傳送10位☸️🧝🏻♂️。每0.5ms可送入1個字符➰,每秒可送入 1s/0.5ms = 2000 個字符🔯。

主頻50MHz,時鐘周期為 1/50MHz = 20ns

0.5ms對應時鐘周期數為 0.5ms/20ns = 25000

傳送1個字符需要的時鐘周期數為 25000 + 10 + 15×4 = 25070

傳送1000個字符需要的時鐘周期數為 25070×1000 = 25070000

CPU用于該任務的時間大約為 1000×(10+20×4)= 9×1 0 4 10^4104 個時鐘周期

中斷隱指令:

關中斷

保存斷點(PC)

引出中斷服務程序

三、DMA 方式

DMA控制器與主存每次傳送1個字👨👧。當傳送完一整塊數據後才向CPU發出中斷請求♗。

1)接受外設發出的DMA請求(外設傳送一個字的請求),並向CPU發出總線請求👩🏼🍳。

2)CPU響應此總線請求🧏🏽♂️,發出總線響應信號🔭,接管總線控制權,進入DMA操作周期。

3)確定傳送數據的主存單元地址及長度,並能自動修改主存地址計數和傳送長度計數💁🏻。

4)規定數據在主存和外設間的傳送方向⛹🏽,發出讀寫等控制信號🧑🏼🦰,執行數據傳送操作⇢。

5)向CPU報告DMA操作的結束。

注:1、2屬于傳送前🤍,3、4屬于傳送時,5屬于傳送後。

1. DMA控制器

注➗:在DMA傳送過程中,DMA控制器將接管CPU的地址總線📑、數據總線和控制總線,CPU的主存控制信號被禁止使用🏌🏿♂️。而當DMA傳送結束後🟩,將恢複CPU的一切權利並開始執行其操作🧓🧸。

2. DMA傳送過程

主存和DMA控制器之間有一條數據通路,因此主存和I/O設備之間交換信息時,不通過CPU♈️。但當I/O設備和CPU同時訪問主存時,可能發生沖突,為了有效地使用主存,DMA控制器與CPU通常采用以下3種方法使用主存𓀅🧝。

3. DMA方式的特點

主存和DMA接口之間有一條直接數據通路。

由于DMA方式傳送數據不需要經過CPU,因此不必中斷現行程序🧝♀️,I/O與主機並行工作,程序和傳送並行工作。

DMA方式具有下列特點:

① 它使主存與CPU的固定聯系脫鉤,主存既可被CPU訪問,又可被外設訪問🤙🏼。

② 在數據塊傳送時,主存地址的確定✍🏼、傳送數據的計數等都由硬件電路直接實現。

③ 主存中要開辟專用緩沖區,及時供給和接收外設的數據。

④ DMA傳送速度快👱🏻♂️,CPU和外設並行工作,提高了系統效率。

⑤ DMA在傳送開始前要通過程序進行預處理🧑🏿💼,結束後要通過中斷方式進行後處理😥。

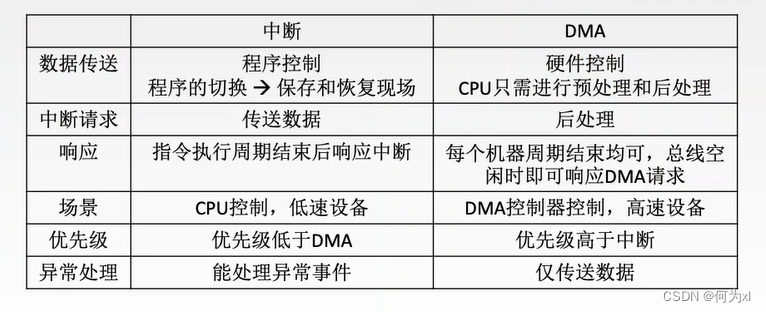

4. DMA方式與中斷方式

鏈接:https://blog.csdn.net/weixin_43848614/article/details/127196419

作者:何為xl